VerilogA采样保持电路模型

改进了采样保持电路VerilogA代码,使其支持模拟沟道电荷注入效应

·

模型考虑到了采样开关RC延时以及,沟道电荷泄露的非理想因素

采样保持电路

原代码:

// VerilogA for SampleAndHold

`include "constants.vams"

`include "disciplines.vams"

module VerilogA_SampleAndHold(clk,vin,vmin,vout);

parameter real vtrans=0.5;

parameter real delay = 0;

parameter real ttime = 1p;

parameter real clk_threshold = 0.5; //vdd is 1v

input clk,vin,vmin;

output vout;

electrical vout,vin,vmin,clk;

real v;

analog begin

// Sampling Phase (+1 is for rising edge, -1 is for falling edge)

@(cross(V(clk) - clk_threshold, +1))

v = V(vin);

V(vout) <+ transition(v,delay,ttime);

end

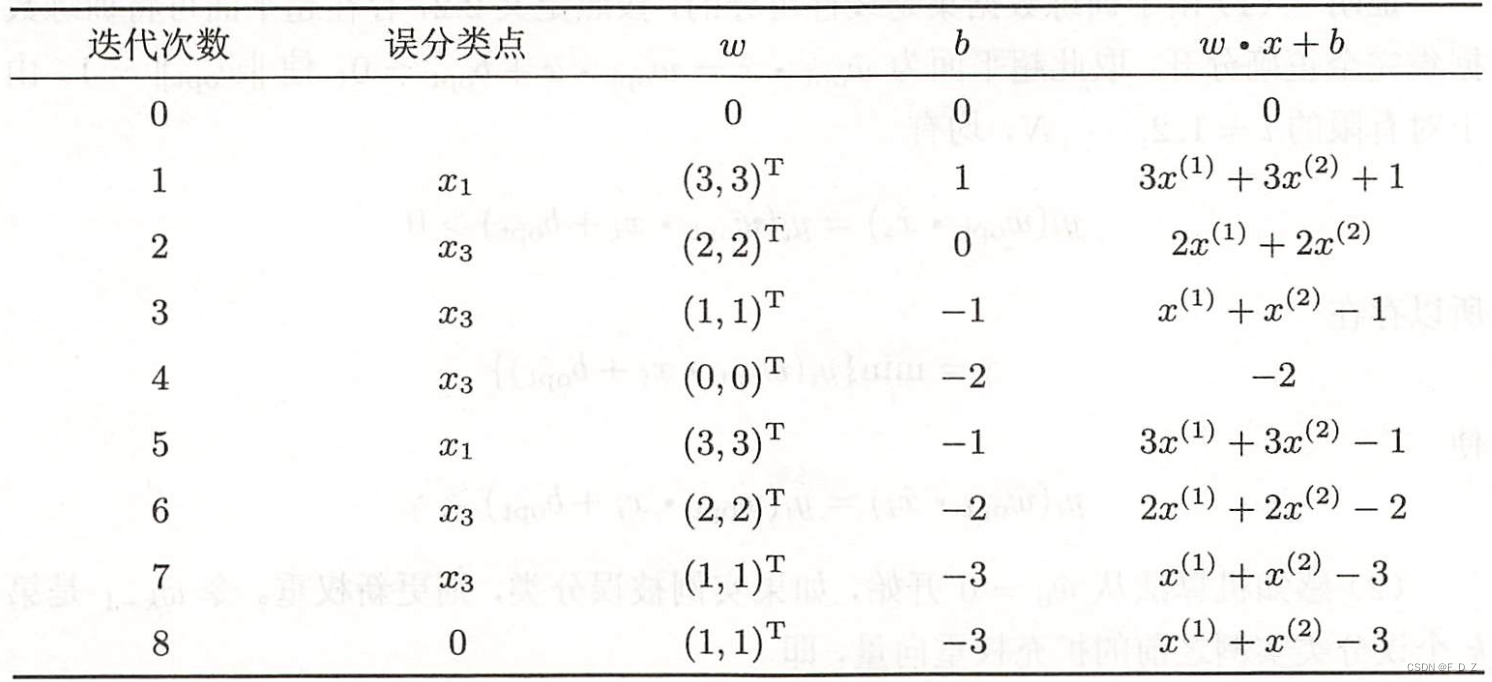

endmodule非理想因素:由于导通电阻和保持电容充放电RC延时

修改参数ttime,改变跟随斜率

原代码存在只跟随脉冲上升沿数值,没有模拟沟道电荷注入效应影响

改进了VerilogA代码,使其支持模拟沟道电荷注入效应

// VerilogA for SampleAndHold

`include "constants.vams"

`include "disciplines.vams"

module VerilogA_SampleAndHold(clk,vin,vmin,vout);

parameter real vtrans=0.5;

parameter real delay = 0;

parameter real ttime = 0.2n;

parameter real clk_threshold = 0.5; //vdd is 1v

parameter real charge_injection_value = 0.01;

input clk,vin,vmin;

output vout;

electrical vout,vin,vmin,clk;

real v;

real T_time;

analog begin

if (V(clk) - clk_threshold > 0 ) begin

v = V(vin);

T_time = ttime;

end

@(cross(V(clk) - clk_threshold, -1))

begin

v = V(vout) - charge_injection_value;

T_time = ttime/100;

end

V(vout) <+ transition(v,delay,T_time);

end

endmodule参数charge_injection_value即为沟道电荷注入效应的影响

改进后仿真结果如下

对采样结果频谱分析

Fin = 2,734,375Hz Fs = 200MHz DFT采样点数512

GitCode 天启AI是一款由 GitCode 团队打造的智能助手,基于先进的LLM(大语言模型)与多智能体 Agent 技术构建,致力于为用户提供高效、智能、多模态的创作与开发支持。它不仅支持自然语言对话,还具备处理文件、生成 PPT、撰写分析报告、开发 Web 应用等多项能力,真正做到“一句话,让 Al帮你完成复杂任务”。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)