Allegro-设置差分对-走线/等长规则

P和N,分别是Positive(+)和Negative(-),有时候M=N,比如USB的DM(Data Minus数据负)(Engineering Query工程询问),你把需要控制阻抗的线,高亮+截图,距离>3W线宽规则,是指相邻线,线中心to线中心距离大于三倍线宽(既Gap=2*Line width)1.自己用SI9000工具去计算(根据层叠,铜厚,介质厚度等等因素加入模型中,去计算生成结果)

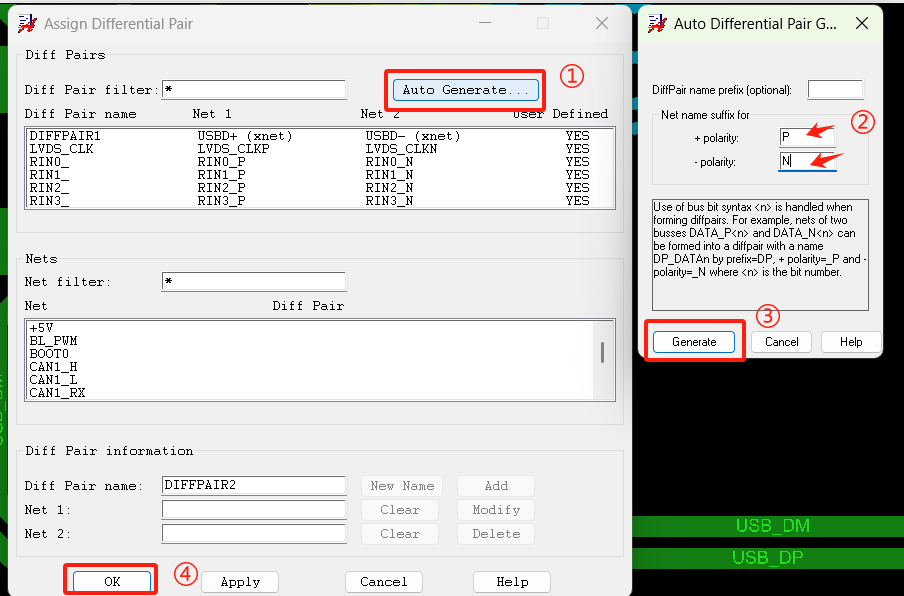

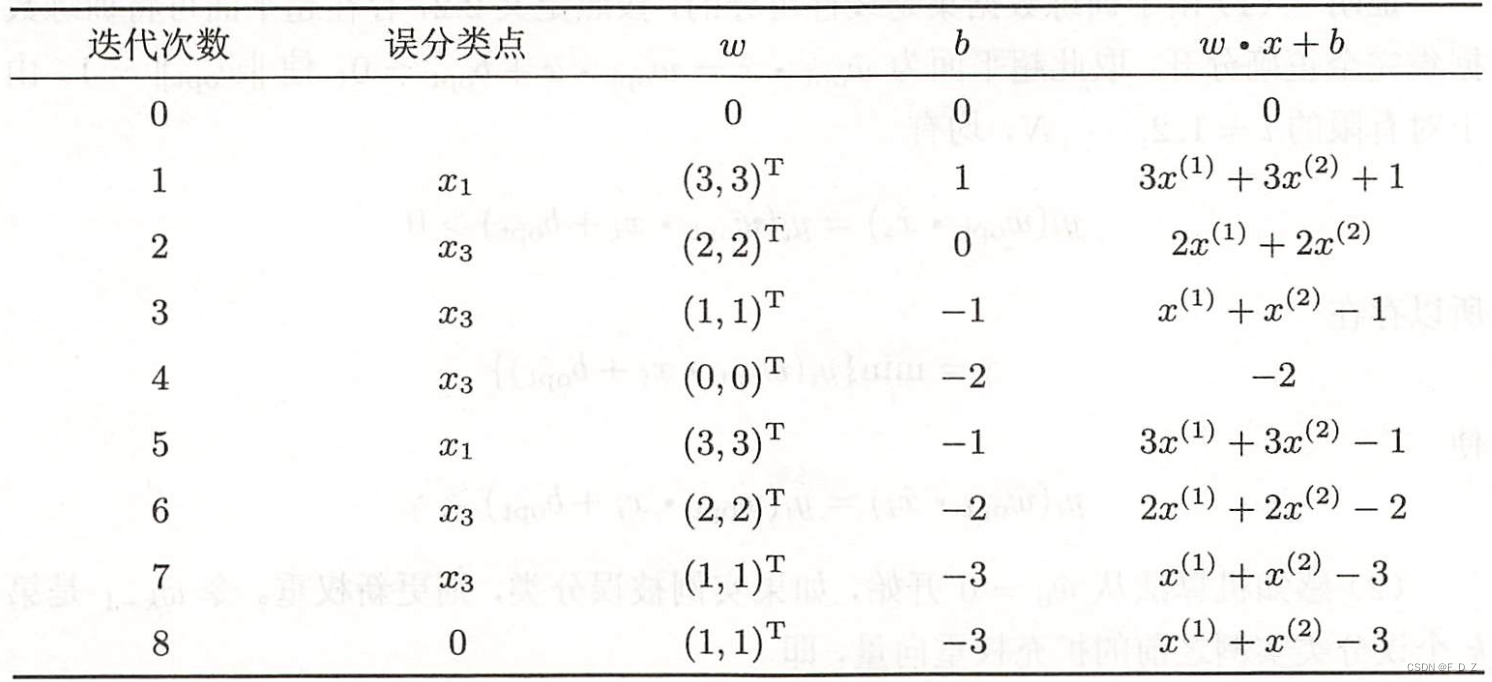

一)设置差分对,有两种方法:

- 自动匹配

- 手动添加

设计时候往往两者相结合,都会用到。

步骤:

①系统自动匹配差分对

②手动添加差分对

差分对设置完毕。

备注:

P和N,分别是Positive(+)和Negative(-),有时候M=N,比如USB的DM(Data Minus数据负)

题外话:LED管或者背光正负极,是A(正极),K(负极).

二)差分对规则

- 差分线物理规则 (线宽/线距)

- 对内等长规则 (Electrical-电气规则)

先说差分线-物理规则,这里特指的是差分线的-线宽-线距规则设置(Physical和Spacing)

1.差分线物理规则

(以USB2.0的DP/DM为例子)

问题一:阻抗要控多少Ω,线宽线距要怎么计算?

问题二:计算好后怎么设置成规则?

问题一:(计算)

USB走线阻抗要控制多少Ω,常规经验:

| 单端 | 50Ω | eg:DDR的单端 数据线,地址线... |

| 差分 | 90Ω | eg:USB线(常识要背)... |

| 100Ω | eg:MIPI ,LVDS, DQS,CLK..... |

知道了USB要控制90Ω,要怎么去算线宽线距?

1.自己用SI9000工具去计算(根据层叠,铜厚,介质厚度等等因素加入模型中,去计算生成结果)

2.丢给制板厂去计算(虽然不道德,但是快乐呀! )

悄咪咪告诉你:差分线的线宽线距加起来等于13mil,工厂啥阻抗都调的出来。13法则!

PCB 厂家在收到客户提供的 Gerber 文件等设计资料后,会对其进行审核,

因此,会有个EQ环节。(Engineering Query工程询问),你把需要控制阻抗的线,高亮+截图,

然后发给板厂,或者给Gerber时候就把工艺说明写好word给板厂。

问题二:(实操)

假如我们通过SI9000计算,或者通过嘉立创阻抗神器,算出USB的90Ω走线:

| Line Width(线宽): | 9mil |

| Gap(间隙): | 4mil |

| shape to line Spacing:(共面铜到差分线距离) | 8mil |

设置步骤:

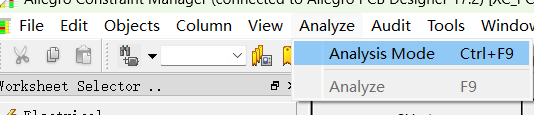

点击规则管理器

以上是针对≥四层板。两层板就不用控制阻抗了,兄弟们。

啥,你问我为什么两层板不用控制阻抗?

两层板走一条50Ω单端线,要几十mill线宽,板子还画个屁哦,省省心啦~

冷知识:

Gap是线边缘to线边缘的距离(两线间隙)

距离>3W线宽规则,是指相邻线,线中心to线中心距离大于三倍线宽(既Gap≥2*Line width)

Neck:是瓶颈模式下,走线的最小线宽

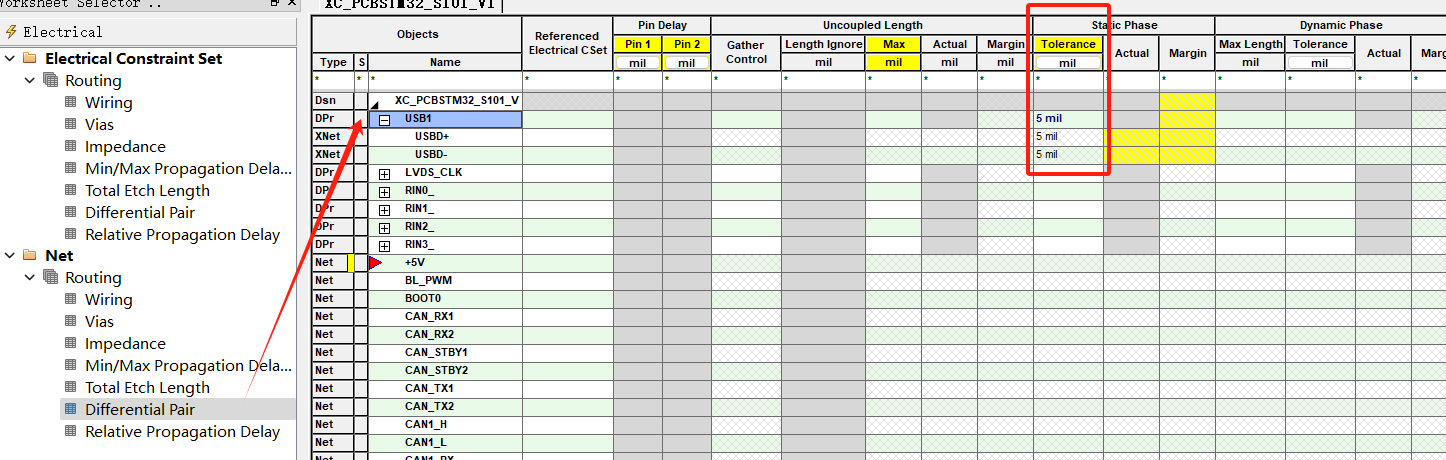

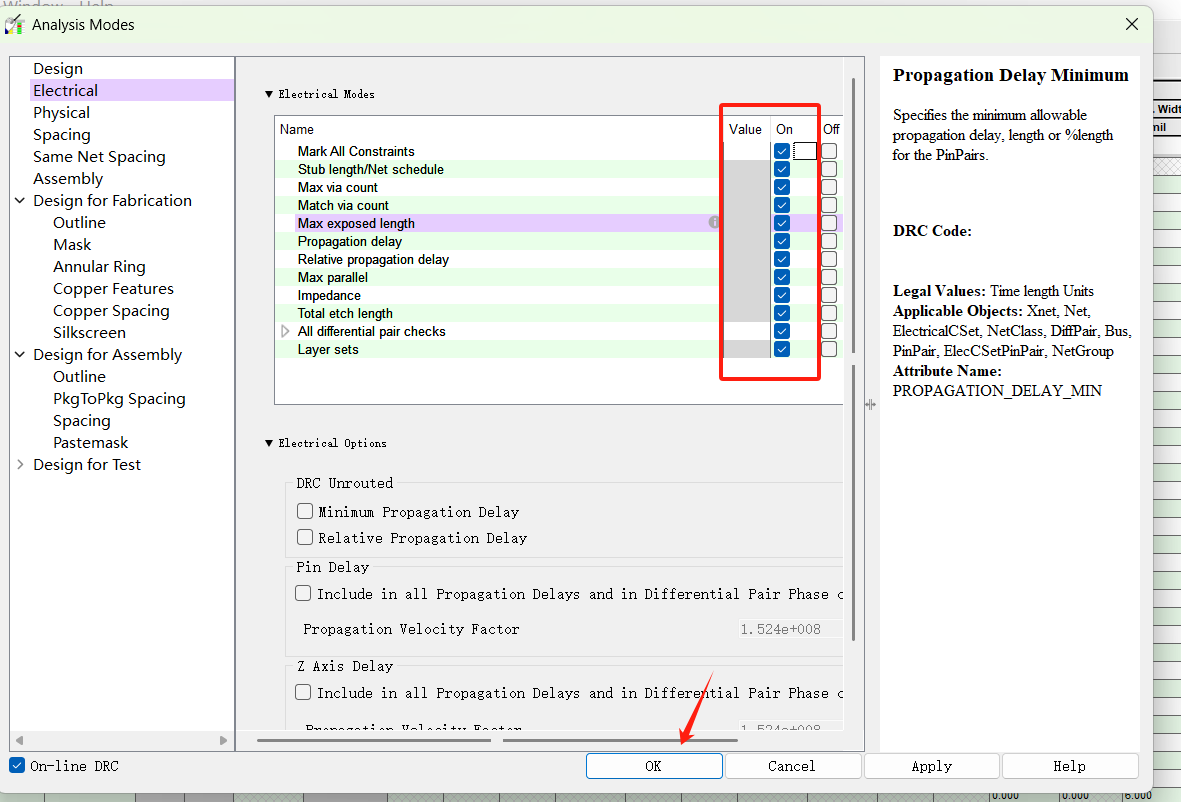

2.对内等长规则

为了差分对耦合紧密,我们需要对差分线设置对内误差规则,假如是设置5mil。

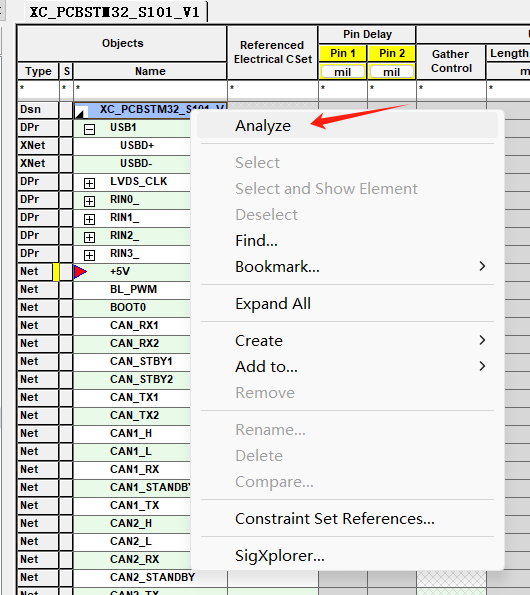

误差设置是5mil,右键更新下

如果更新失败

规则设置完毕,报红就去绕线吧!哈哈哈哈~

以上就是差分对相关设置啦~

课后思考:

1.怎么处理Xnet走线规则异常问题

2.差分对组间等长怎么设置

3.相对等长和绝对等长有什么区别

GitCode 天启AI是一款由 GitCode 团队打造的智能助手,基于先进的LLM(大语言模型)与多智能体 Agent 技术构建,致力于为用户提供高效、智能、多模态的创作与开发支持。它不仅支持自然语言对话,还具备处理文件、生成 PPT、撰写分析报告、开发 Web 应用等多项能力,真正做到“一句话,让 Al帮你完成复杂任务”。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)