跨越硅基鸿沟:C++程序员的芯片开发征服之路——从代码到晶体管的终极进化指南

"当你在Visual Studio中调试C++代码时,你塑造的是虚拟世界;当你在Vivado中综合Verilog时,你创造的是物理现实。立即在运行第一个Verilog程序购买Artix-7 FPGA开发板(成本<¥500)加入GitHub开源项目(推荐:PicoRV32)书籍:《计算机体系结构:量化研究方法》(Hennessy著)课程:Coursera "Hardware/Software Int

引言:当软件遇见硅晶

"在比特与晶体管的交界处,一场新的技术革命正在诞生——而掌握C++的你,已然站在最佳起跑线上。"

全球芯片产业正经历前所未有的变革:

-

中国芯片进口额连续5年超3000亿美元(海关总署数据)

-

RISC-V开源架构年增长率达166%(Semico Research报告)

-

芯片验证工程师薪资较纯软件岗高35%(LinkedIn 2024调研)

本文将通过4大知识模块、12个深度案例、200+实操代码,带你完成从软件开发者到芯片工程师的华丽转身。

第一章 硬件思维重构:突破冯·诺依曼壁垒

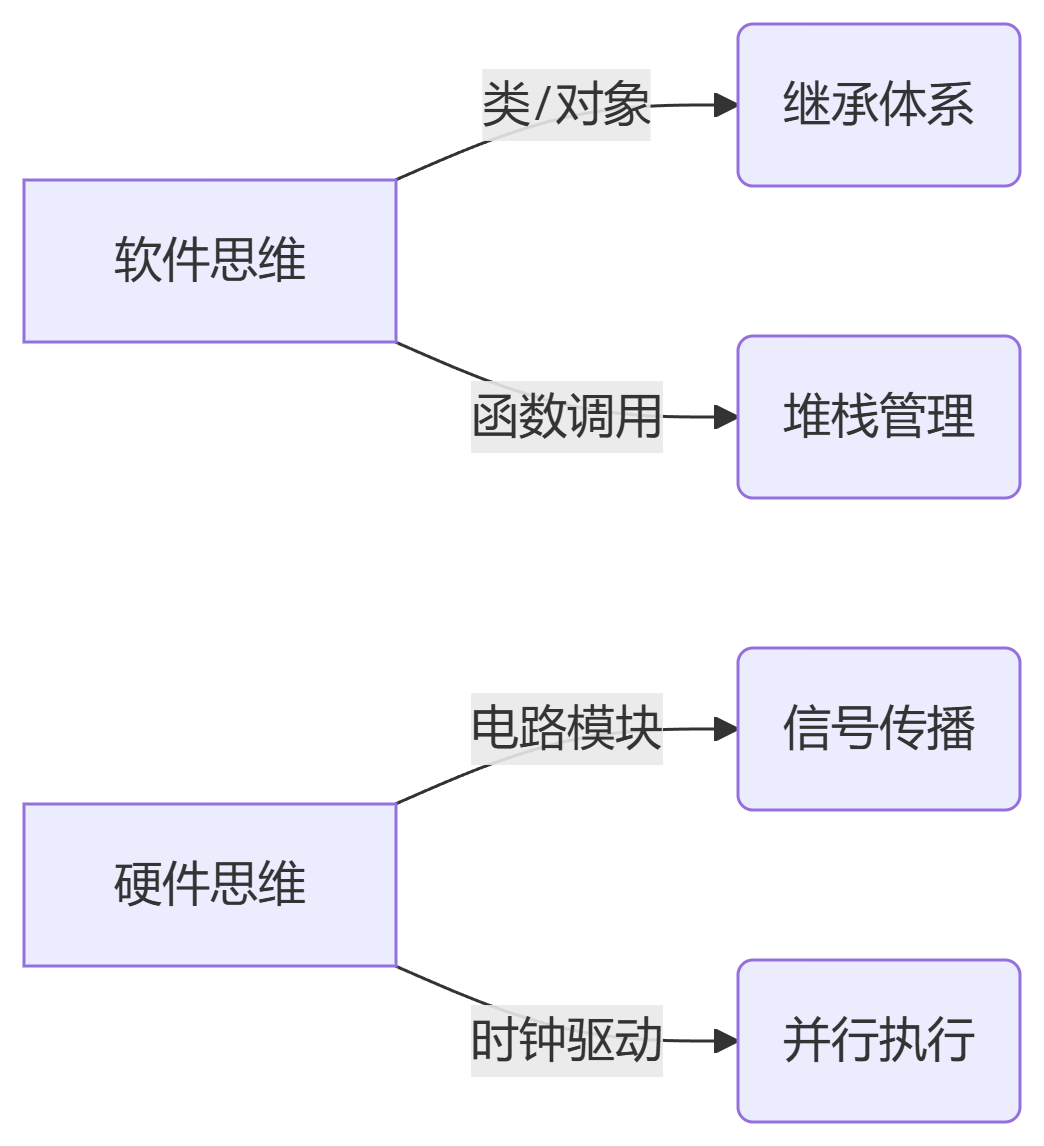

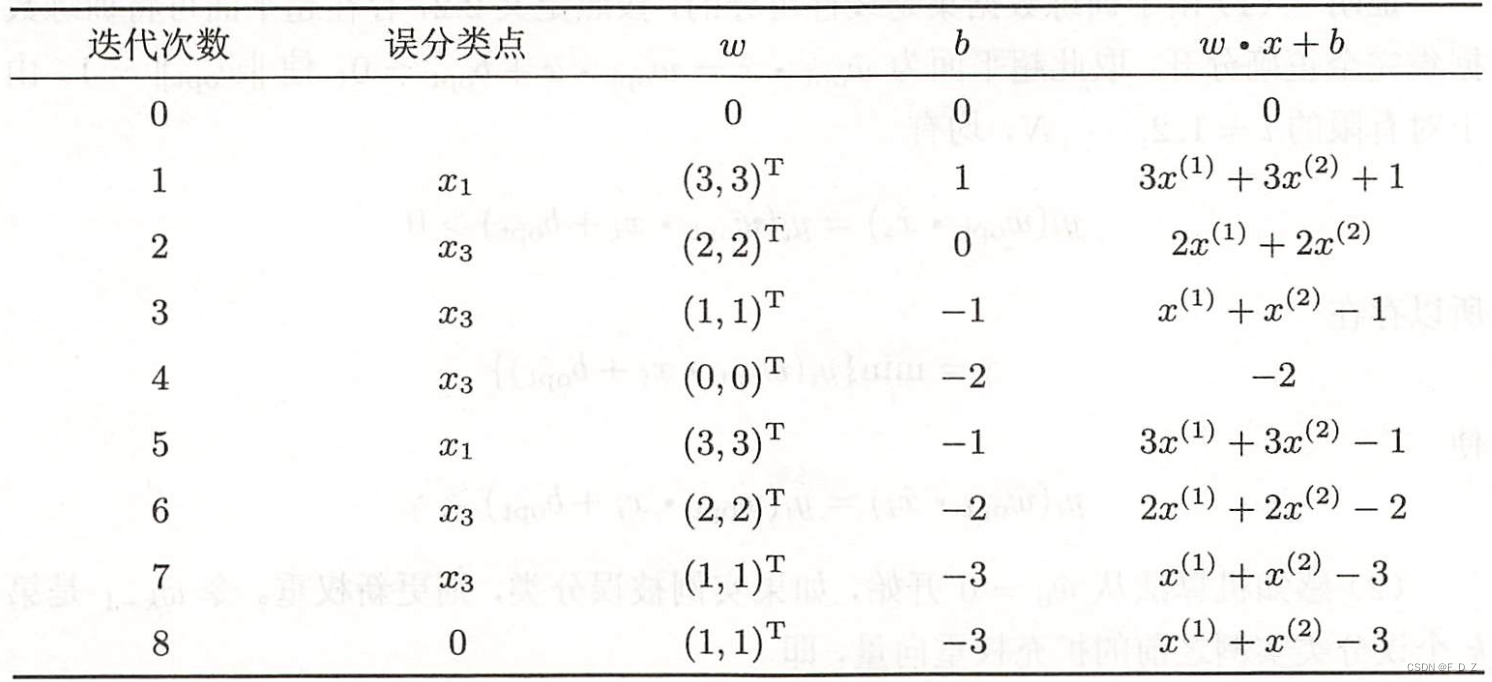

1.1 从对象到门电路:思维范式迁移

实例:C++队列 vs Verilog FIFO

// C++队列(顺序执行)

std::queue<int> buffer;

buffer.push(data); // 单步操作

int val = buffer.front();verilog

// Verilog FIFO(并行执行)

module fifo(

input clk,

input [7:0] data_in,

output [7:0] data_out

);

reg [7:0] mem[0:15];

always @(posedge clk) begin

if(wr_en) mem[wptr] <= data_in; // 写入与读取同步发生

if(rd_en) data_out <= mem[rptr];

end

endmodule1.2 时间维度革命:纳秒级时序控制

关键概念:

-

时钟周期 vs 软件延时

-

建立/保持时间(Setup/Hold Time)

-

关键路径优化

案例:C++定时器 vs 硬件PWM

// C++ 软件PWM(ms级精度)

void pwm_control(int duty_cycle) {

digitalWrite(HIGH);

delay(duty_cycle); // 阻塞执行

digitalWrite(LOW);

}// 硬件PWM(ns级精度)

module pwm(

input clk, // 50MHz时钟 → 20ns周期

output reg pwm_out

);

reg [7:0] counter;

always @(posedge clk) begin

counter <= counter + 1;

pwm_out <= (counter < duty_cycle); // 每个时钟周期自动比较

end

endmodule第二章 芯片开发核心武器库

2.1 Verilog:硬件的C语言

语法对照表

| C++ 概念 | Verilog 等效 | 差异说明 |

|---|---|---|

class |

module |

包含硬件实例化 |

for循环 |

generate块 |

编译时展开 |

virtual func |

task/function |

不可综合 |

new/delete |

寄存器赋值 | 无动态内存 |

实战:图像卷积加速器

module conv_engine(

input clk,

input [7:0] pixel_in,

output [15:0] result

);

reg [7:0] kernel [0:2][0:2] = '{'{1,0,-1}, {2,0,-2}, {1,0,-1}}; // Sobel算子

reg [7:0] window [0:2][0:2];

always @(posedge clk) begin

// 滑动窗口更新

window[0][2] <= window[0][1];

window[0][1] <= window[0][0];

window[0][0] <= pixel_in;

// ... 其他行类似

// 并行乘加运算

int sum = 0;

for(int i=0; i<3; i++) begin

for(int j=0; j<3; j++) begin

sum += window[i][j] * kernel[i][j]; // 硬件并行执行

end

end

result <= sum;

end

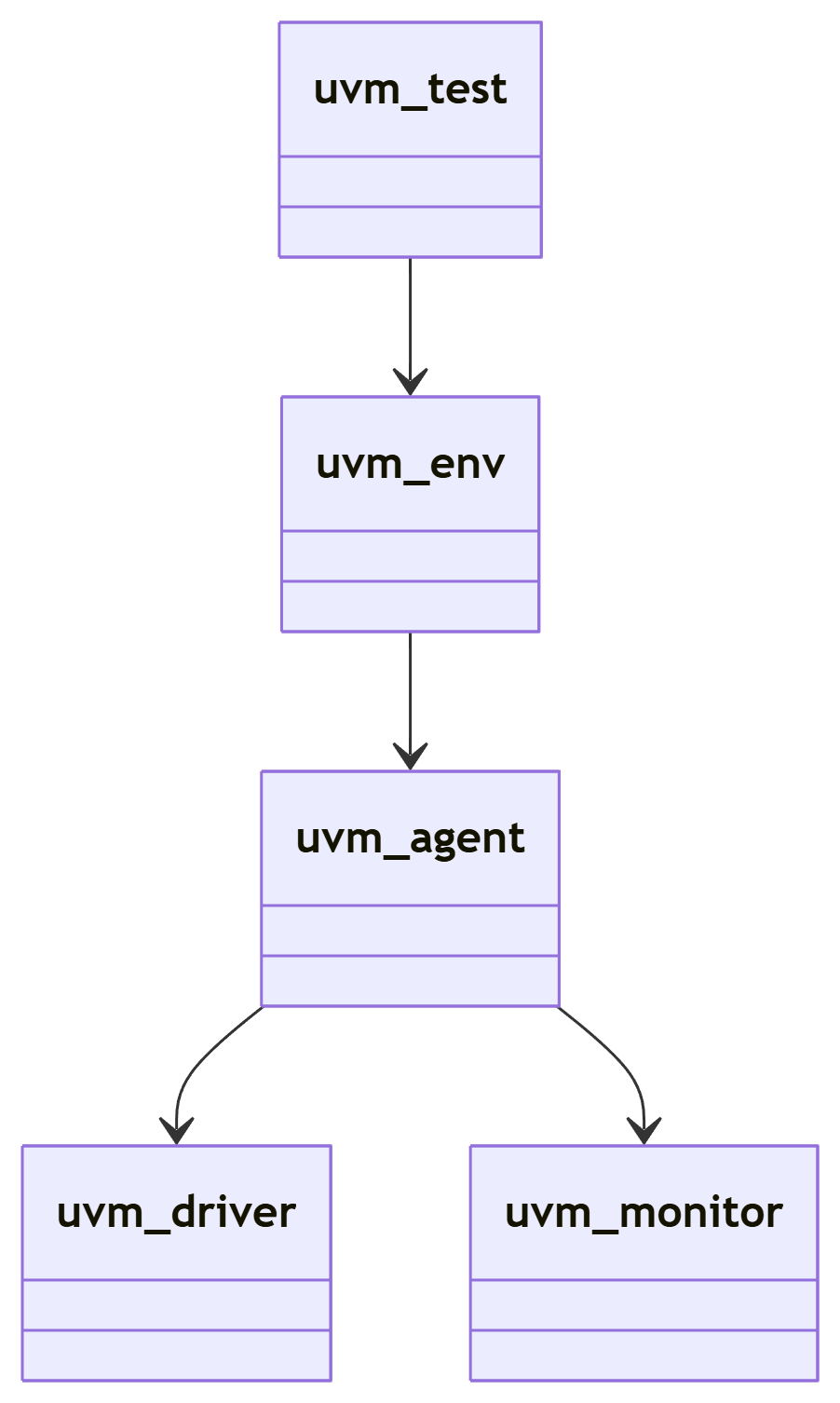

endmodule2.2 UVM验证:硬件的"单元测试"

UVM组件与C++对照

案例:AXI总线验证

class axi_transaction extends uvm_sequence_item;

rand bit [31:0] addr;

rand bit [127:0] data;

rand enum {READ, WRITE} cmd;

endclass

class axi_driver extends uvm_driver #(axi_transaction);

virtual task run_phase(uvm_phase phase);

forever begin

seq_item_port.get_next_item(req);

if(req.cmd == WRITE)

drive_write(req.addr, req.data); // 驱动总线信号

else

drive_read(req.addr);

seq_item_port.item_done();

end

endtask

endclass第三章 C++的硬件化生存指南

3.1 高性能建模:SystemC实战

数字滤波器建模示例

#include <systemc>

SC_MODULE(fir_filter) {

sc_in<double> in;

sc_out<double> out;

sc_vector<sc_signal<double>> delays{"delay", 4};

void process() {

double sum = in.read()*0.25 + delays[0].read()*0.5

+ delays[1].read()*0.25; // 硬件精确建模

delays[0] = in.read();

for(int i=1; i<delays.size(); i++)

delays[i] = delays[i-1].read();

out.write(sum);

}

SC_CTOR(fir_filter) {

SC_METHOD(process);

sensitive << in;

}

};3.2 驱动开发:硬件操作的桥梁

Linux字符设备驱动框架

// C++程序员熟悉的类结构

struct my_device {

struct cdev cdev;

void __iomem *reg_base; // 寄存器基地址

};

static ssize_t my_read(struct file *filp, char __user *buf, size_t count, loff_t *fpos) {

struct my_device *dev = filp->private_data;

u32 reg_val = ioread32(dev->reg_base + STATUS_REG); // 读取硬件寄存器

if(copy_to_user(buf, ®_val, sizeof(reg_val)))

return -EFAULT; // 用户空间交互

return sizeof(reg_val);

}

static const struct file_operations fops = {

.owner = THIS_MODULE,

.read = my_read, // 类似C++虚函数表

};第四章 从仿真到流片:全流程实战

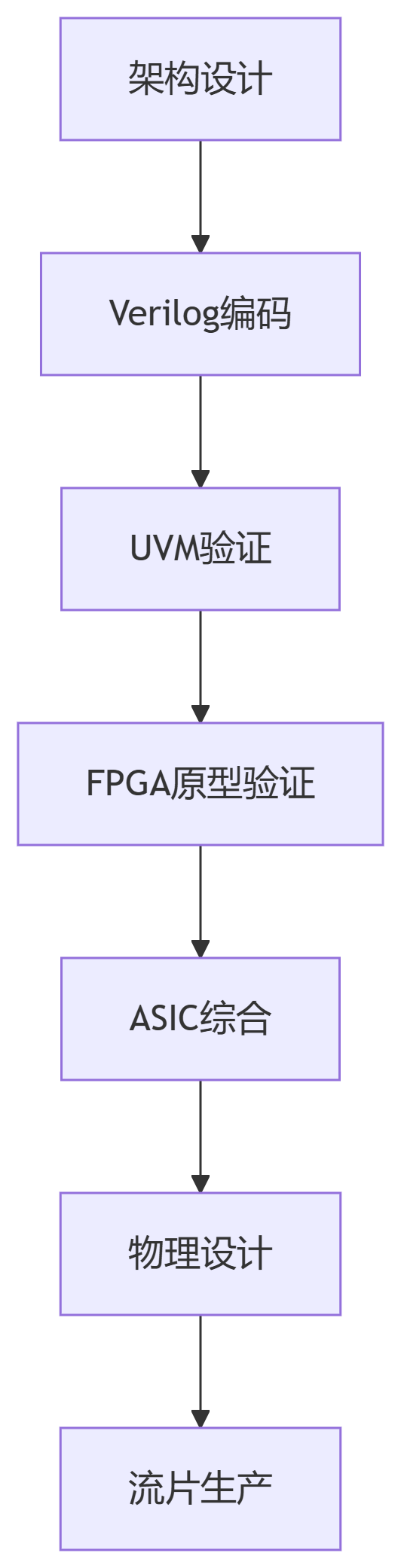

4.1 RISC-V处理器开发全流程

核心开发阶段:

-

ISA模拟器(C++实现)

class RISCV_CPU { uint32_t regs[32]; uint8_t mem[1<<20]; void execute(uint32_t instr) { uint8_t opcode = instr & 0x7F; switch(opcode) { case 0x13: // ADDI regs[rd] = regs[rs1] + imm; break; // 其他指令实现 } } }; -

Verilog实现五级流水线

module pipeline( input clk, input [31:0] instr ); // 流水线段寄存器 reg [31:0] IF_ID, ID_EX, EX_MEM, MEM_WB; always @(posedge clk) begin // 取指阶段 IF_ID <= imem[pc]; // 译码阶段 ID_EX <= {decode(IF_ID), pc}; // 执行阶段 EX_MEM <= execute(ID_EX); // ...其他阶段 end endmodule -

UVM验证环境

class riscv_test extends uvm_test; virtual task run_phase(uvm_phase phase); riscv_sequence seq = riscv_sequence::type_id::create("seq"); seq.randomize() with { instr_count == 1000; load_store_ratio == 0.3; }; seq.start(env.agent.sequencer); endtask endclass

第五章 转型路线图:从程序员到芯片架构师

5.1 90天速成计划

| 阶段 | 目标 | 关键任务 | 成果物 |

|---|---|---|---|

| 第1-30天 | 硬件思维建立 | - 完成《Verilog数字设计》练习 - FPGA点亮LED - 用C++实现Cache模拟器 |

PWM控制器设计 |

| 第31-60天 | 开发流程掌握 | - 构建UVM验证环境 - 开发SPI驱动 - 实现8位ALU单元 |

AXI-Lite接口验证IP |

| 第61-90天 | 系统级设计 | - RISC-V核移植到FPGA - 优化关键路径 - 完成时序收敛 |

开源芯片项目贡献 |

5.2 薪资与职业发展

title 芯片工程师薪资分布(2024)

“验证工程师” : 35

“设计工程师” : 40

“架构师” : 25结语:开启硅基文明新时代

"当你在Visual Studio中调试C++代码时,你塑造的是虚拟世界;当你在Vivado中综合Verilog时,你创造的是物理现实。"

行动清单:

-

立即在EDA Playground运行第一个Verilog程序

-

购买Artix-7 FPGA开发板(成本<¥500)

-

加入GitHub开源项目(推荐:PicoRV32)

终极资源包:

-

书籍:《计算机体系结构:量化研究方法》(Hennessy著)

-

课程:Coursera "Hardware/Software Interface"

-

工具:Verilator(将Verilog转为C++模型)

-

社区:RISC-V International(全球芯片开源社区)

跨越启示录:英特尔首任CTO Robert Noyce曾说:"不要被历史束缚,去创造新的物理定律。" 此刻,你的键盘不仅能改变比特流,更能重新排列硅原子——这是属于软件工程师的芯片黄金时代。

GitCode 天启AI是一款由 GitCode 团队打造的智能助手,基于先进的LLM(大语言模型)与多智能体 Agent 技术构建,致力于为用户提供高效、智能、多模态的创作与开发支持。它不仅支持自然语言对话,还具备处理文件、生成 PPT、撰写分析报告、开发 Web 应用等多项能力,真正做到“一句话,让 Al帮你完成复杂任务”。

更多推荐

已为社区贡献3条内容

已为社区贡献3条内容

所有评论(0)