【cache prefetch】

https://en.wikipedia.org/wiki/Cache_prefetching文章目录1. Data vs. instruction cache prefetching2. Hardware vs. software cache prefetching3. Methods of hardware prefetching3.1 stream buffers3.2 stride pre

文章目录

1. Data vs. instruction cache prefetching

- data prefetch:数据访问模式比指令模式表现出来的规律性更小,准确的数据预取比指令预取更具有挑战性。

- instruction prefetch:在需要执行之前fetch指令

2. Hardware vs. software cache prefetching

- Hardware based prefetch: 基于硬件的预取通常是通过在处理器中有一个专用的硬件机制来完成的,该机制监视执行程序请求的指令流或数据流,根据该流识别程序可能需要的下几个元素,并预取到处理器的缓存中。

- Software based prefetch:基于软件的预取通常是通过让编译器在编译过程中分析代码并在程序中插入额外的“预取”指令来完成的。

3. Methods of hardware prefetching

3.1 stream buffers

流缓冲区,与缓存分离。

顺序预取,sequential prefetch.

这种机制可以通过添加多个流缓冲区(stream buffers)来扩展——每个缓冲区将维护一个单独的预取流。对于每个新的未命中,将分配一个新的流缓冲区,并且它将以与上述类似的方式运行。

流缓冲区的理想深度取决于各种基准测试,并取决于所涉及的其他微体系结构。

3.2 stride prefetching

这种类型的预取监控内存访问地址之间的增量,并在其中寻找模式。

- regular strides. 对相隔s个地址的块进行连续的内存访问。prefetcher计算s,并使用它计算预取的内存地址。

- Irregular strides. 连续内存访问地址之前的增量是可变的,但仍然遵循一种模式。

3.3 Temporal prefetch

这类预取器寻找随时间重复的内存访问流。例如,在这个内存访问流中:N,A,B,C,E,G,H,A,B,C,I,J,K,A,B,C,L,M,N,O,A,B,C…;流A、B、C会随着时间的推移而重复。其他设计变体试图提供更高效、更高性能的实现。

3.4 Collaborative prefetching

计算机应用程序生成各种访问模式。用于执行这些应用程序的处理器和内存子系统架构进一步消除了它们生成的内存访问模式的歧义。因此,预取方案的有效性和效率通常取决于应用程序和用于执行它们的体系结构。最近的研究集中于建立协作机制,协同使用多个预取方案,以实现更好的预取覆盖率和准确性。

4. Methods of software prefetching

compiler directed prefetching

编译器导向的预取广泛应用于大量迭代的循环中。在这种技术中,编译器预测未来的缓存未命中,并根据miss-penalty和指令的执行时间插入预取指令。

这些预取是非阻塞内存操作,即这些内存访问不会干扰实际内存访问。它们不会改变处理器的状态或导致页面错误。

软件预取的一个主要优点是减少了强制缓存未命中的次数。可以将预取指令添加到代码中以提高缓存性能。

5. comparison of hardware and software prefetching

- 虽然软件预取需要程序员或编译器的干预,但硬件预取需要特殊的硬件机制。

- 软件预取仅适用于有规则数组访问的循环,因为程序员必须手工编写预取指令,而硬件预取器则根据程序在运行时的行为动态工作。

- 与软件预取相比,硬件预取的CPU开销也更小。

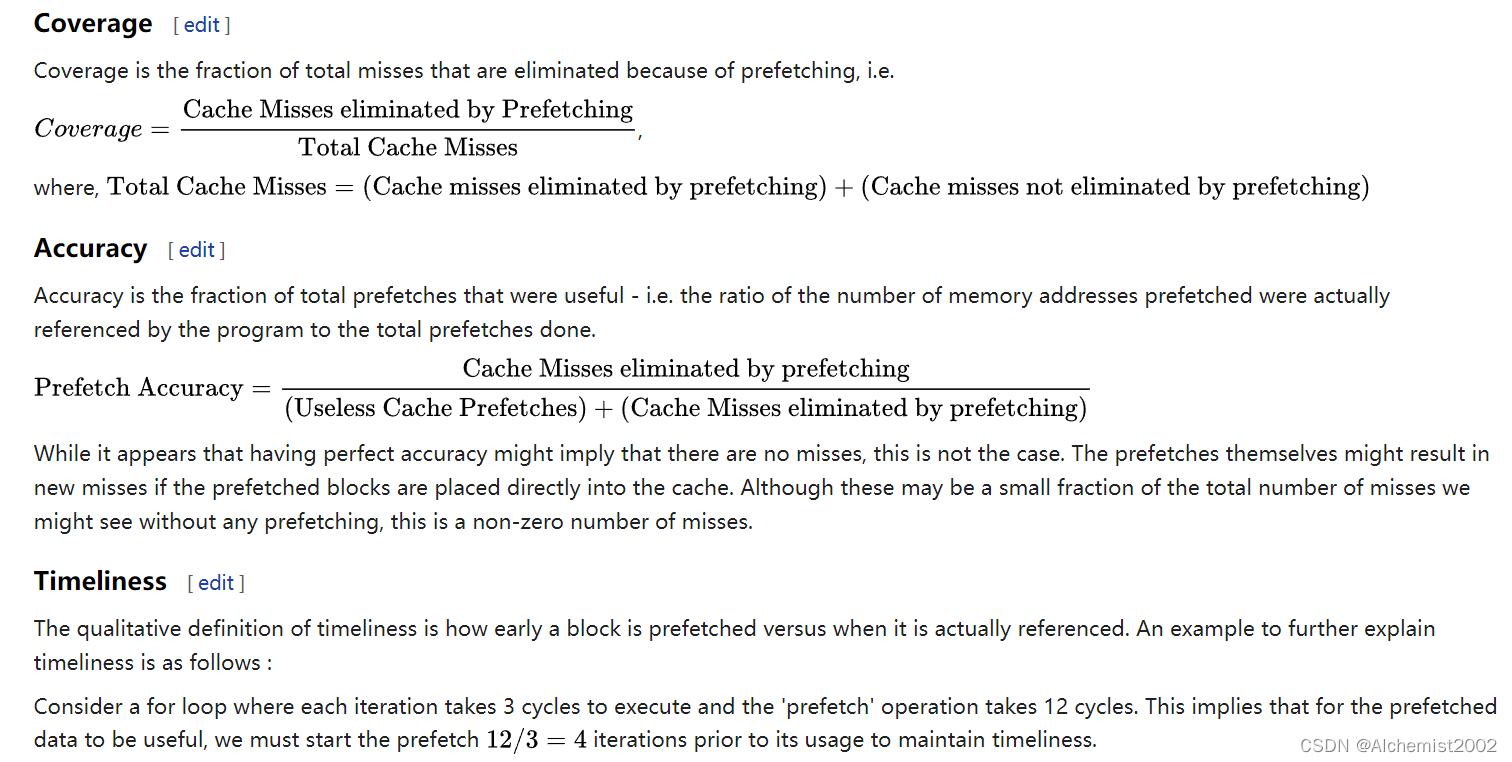

6. Metrices of cache prefetching

GitCode 天启AI是一款由 GitCode 团队打造的智能助手,基于先进的LLM(大语言模型)与多智能体 Agent 技术构建,致力于为用户提供高效、智能、多模态的创作与开发支持。它不仅支持自然语言对话,还具备处理文件、生成 PPT、撰写分析报告、开发 Web 应用等多项能力,真正做到“一句话,让 Al帮你完成复杂任务”。

更多推荐

已为社区贡献1条内容

已为社区贡献1条内容

所有评论(0)